# Features

- Single 2.5V or 2.7V to 3.6V Supply

- RapidS<sup>®</sup> Serial Interface: 66 MHz Maximum Clock Frequency

SPI Compatible Modes 0 and 3

- User Configurable Page Size

- 256 Bytes per Page

- 264 Bytes per Page

- Page Size Can Be Factory Pre-configured for 256 Bytes

- Page Program Operation

- Intelligent Programming Operation

- 2,048 Pages (256/264 Bytes/Page) Main Memory

- Flexible Erase Options

- Page Erase (256 Bytes)

- Block Erase (2 Kbytes)

- Sector Erase (64 Kbytes)

- Chip Erase (4 Mbits)

- Two SRAM Data Buffers (256/264 Bytes)

- Allows Receiving of Data while Reprogramming the Flash Array

- Continuous Read Capability through Entire Array

- Ideal for Code Shadowing Applications

- Low-power Dissipation

- 7 mA Active Read Current Typical

- 25 µA Standby Current Typical

- 5 μA Deep Power-down Typical

- Hardware and Software Data Protection Features

- Individual Sector

- Sector Lockdown for Secure Code and Data Storage – Individual Sector

- Security: 128-byte Security Register

- 64-byte User Programmable Space

- Unique 64-byte Device Identifier

- JEDEC Standard Manufacturer and Device ID Read

- 100,000 Program/Erase Cycles Per Page Minimum

- Data Retention 20 Years

- Industrial Temperature Range

- Green (Pb/Halide-free/RoHS Compliant) Packaging Options

# 1. Description

The AT45DB041D is a 2.5V or 2.7V, serial-interface Flash memory ideally suited for a wide variety of digital voice-, image-, program code- and data-storage applications. The AT45DB041D supports RapidS serial interface for applications requiring very high speed operations. RapidS serial interface is SPI compatible for frequencies up to 66 MHz. Its 4,325,376 bits of memory are organized as 2,048 pages of 256 bytes or 264 bytes each. In addition to the main memory, the AT45DB041D also contains two SRAM buffers of 256/264 bytes each. The buffers allow the receiving of data while a page in the main Memory is being reprogrammed, as well as writing a continuous data stream. EEPROM emulation (bit or byte alterability) is easily handled with a self-contained three step read-modify-write operation. Unlike conventional Flash memories that are accessed randomly with multiple address lines and a parallel interface, the DataFlash uses a RapidS serial interface to sequentially access its data. The simple sequential access dramatically reduces active pin count, facilitates hardware layout,

4-megabit 2.5-volt or 2.7-volt DataFlash<sup>®</sup>

# AT45DB041D

increases system reliability, minimizes switching noise, and reduces package size. The device is optimized for use in many commercial and industrial applications where high-density, low-pin count, low-voltage and low-power are essential.

To allow for simple in-system reprogrammability, the AT45DB041D does not require high input voltages for programming. The device operates from a single power supply, 2.5V to 3.6V or 2.7V to 3.6V, for both the program and read operations. The AT45DB041D is enabled through the chip select pin ( $\overline{CS}$ ) and accessed via a three-wire interface consisting of the Serial Input (SI), Serial Output (SO), and the Serial Clock (SCK).

All programming and erase cycles are self-timed.

### 2. Pin Configurations and Pinouts

| Table 2-1. | Pin Configurations |

|------------|--------------------|

|------------|--------------------|

| Symbol          | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Asserted<br>State | Туре   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|

| <u>cs</u>       | <ul> <li>Chip Select: Asserting the CS pin selects the device. When the CS pin is deasserted, the device will be deselected and normally be placed in the standby mode (not Deep Power-Down mode), and the output pin (SO) will be in a high-impedance state. When the device is deselected, data will not be accepted on the input pin (SI).</li> <li>A high-to-low transition on the CS pin is required to start an operation, and a low-to-high transition is required to end an operation. When ending an internally self-timed operation such as a program or erase cycle, the device will not enter the standby mode until the completion of the operation.</li> </ul> |                   | Input  |

| SCK             | Serial Clock: This pin is used to provide a clock to the device and is used to control the flow of data to and from the device. Command, address, and input data present on the SI pin is always latched on the rising edge of SCK, while output data on the SO pin is always clocked out on the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                        |                   | Input  |

| SI              | Serial Input: The SI pin is used to shift data into the device. The SI pin is used for all data input including command and address sequences. Data on the SI pin is always latched on the rising edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                 | Input  |

| SO              | Serial Output: The SO pin is used to shift data out from the device. Data on the SO pin is always clocked out on the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                 | Output |

| WP              | Write Protect:When the $\overline{WP}$ pin is asserted, all sectors specified for protection by the Sector Protection Register will<br>be protected against program and erase operations regardless of whether the Enable Sector Protection command<br>has been issued or not. The $\overline{WP}$ pin functions independently of the software controlled protection method. After the<br>$\overline{WP}$ pin goes low, the content of the Sector Protection Register cannot be modified.If a program or erase command is issued to the device while the $\overline{WP}$ pin is asserted, the device will simply ignore<br>                                                  | Low               | Input  |

| RESET           | <b>Reset:</b> A low state on the reset pin (RESET) will terminate the operation in progress and reset the internal state machine to an idle state. The device will remain in the reset condition as long as a low level is present on the RESET pin is brought back to a high level                                                                                                                                                                                                                                                                                                                                                                                          |                   | Input  |

| V <sub>CC</sub> | <b>Device Power Supply:</b> The $V_{CC}$ pin is used to supply the source voltage to the device.<br>Operations at invalid $V_{CC}$ voltages may produce spurious results and should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                 | Power  |

| GND             | Ground: The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                 | Ground |

# **18. Electrical Specifications**

Table 18-1.

Absolute Maximum Ratings\*

| Temperature under Bias                                                         |

|--------------------------------------------------------------------------------|

| Storage Temperature                                                            |

| All Input Voltages (including NC Pins)<br>with Respect to Ground0.6V to +6.25V |

| All Output Voltages with Respect to Ground0.6V to $V_{CC}$ + 0.6V              |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 18-2.DC and AC Operating Range

|                              |      | AT45DB041D (2.5V Version) | AT45DB041D      |

|------------------------------|------|---------------------------|-----------------|

| Operating Temperature (Case) | Ind. | -40° C to 85° C           | -40° C to 85° C |

| V <sub>CC</sub> Power Supply |      | 2.5V to 3.6V              | 2.7V to 3.6V    |

#### Table 18-3. DC Characteristics

| Symbol                                                         | Parameter                                                                                                      | Condition                                                                                   | Min                    | Тур | Max                   | Units |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|-------|

| I <sub>DP</sub>                                                | Deep Power-down Current                                                                                        | $\overline{CS}$ , $\overline{RESET}$ , $\overline{WP} = V_{IH}$ , all inputs at CMOS levels |                        | 5   | 10                    | μA    |

| I <sub>SB</sub>                                                | Standby Current $\overline{CS}$ , $\overline{RESET}$ , $\overline{WP} = V_{IH}$ , all<br>inputs at CMOS levels |                                                                                             |                        | 25  | 50                    | μA    |

| I <sub>CC1</sub> <sup>(1)</sup> Active Current, Read Operation | $    f = 20 \text{ MHz}; I_{OUT} = 0 \text{ mA}; $ $    V_{CC} = 3.6 \text{V} $                                |                                                                                             | 7                      | 10  | mA                    |       |

|                                                                | f = 33 MHz; I <sub>OUT</sub> = 0 mA;<br>V <sub>CC</sub> = 3.6V                                                 |                                                                                             | 8                      | 12  | mA                    |       |

|                                                                | $    f = 50 \text{ MHz}; I_{OUT} = 0 \text{ mA}; $ $    V_{CC} = 3.6 \text{V} $                                |                                                                                             | 10                     | 14  | mA                    |       |

|                                                                | $    f = 66 \text{ MHz; } I_{OUT} = 0 \text{ mA;} $ $    V_{CC} = 3.6 \text{V} $                               |                                                                                             | 11                     | 15  | mA                    |       |

| I <sub>CC2</sub>                                               | Active Current, Program/Erase<br>Operation                                                                     | V <sub>CC</sub> = 3.6V                                                                      |                        | 12  | 17                    | mA    |

| ILI                                                            | Input Load Current                                                                                             | V <sub>IN</sub> = CMOS levels                                                               |                        |     | 1                     | μA    |

| I <sub>LO</sub>                                                | Output Leakage Current                                                                                         | V <sub>I/O</sub> = CMOS levels                                                              |                        |     | 1                     | μA    |

| V <sub>IL</sub>                                                | Input Low Voltage                                                                                              |                                                                                             |                        |     | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub>                                                | Input High Voltage                                                                                             |                                                                                             | V <sub>CC</sub> x 0.7  |     |                       | V     |

| V <sub>OL</sub>                                                | Output Low Voltage                                                                                             | I <sub>OL</sub> = 1.6 mA; V <sub>CC</sub> = 2.7V                                            |                        |     | 0.4                   | V     |

| V <sub>OH</sub>                                                | Output High Voltage                                                                                            | I <sub>OH</sub> = -100 μA                                                                   | V <sub>CC</sub> - 0.2V |     |                       | V     |

Notes: 1. I<sub>CC1</sub> during a buffer read is 20 mA maximum @ 20 MHz.

2. All inputs are 5 volts tolerant.

| Symbol                           |                                                         | AT45DB041D<br>(2.5V Version) |     |     | AT45DB041D |     |     |       |

|----------------------------------|---------------------------------------------------------|------------------------------|-----|-----|------------|-----|-----|-------|

|                                  | Parameter                                               | Min                          | Тур | Max | Min        | Тур | Max | Units |

| f <sub>scк</sub>                 | SCK Frequency                                           |                              |     | 50  |            |     | 66  | MHz   |

| f <sub>CAR1</sub>                | SCK Frequency for Continuous Array Read                 |                              |     | 50  |            |     | 66  | MHz   |

| f <sub>CAR2</sub>                | SCK Frequency for Continuous Array Read (Low Frequency) |                              |     | 33  |            |     | 33  | MHz   |

| t <sub>wH</sub>                  | SCK High Time                                           | 6.8                          |     |     | 6.8        |     |     | ns    |

| t <sub>WL</sub>                  | SCK Low Time                                            | 6.8                          |     |     | 6.8        |     |     | ns    |

| t <sub>SCKR</sub> <sup>(1)</sup> | SCK Rise Time, Peak-to-Peak (Slew Rate)                 | 0.1                          |     |     | 0.1        |     |     | V/ns  |

| t <sub>SCKF</sub> <sup>(1)</sup> | SCK Fall Time, Peak-to-Peak (Slew Rate)                 | 0.1                          |     |     | 0.1        |     |     | V/ns  |

| t <sub>cs</sub>                  | Minimum CS High Time                                    | 50                           |     |     | 50         |     |     | ns    |

| t <sub>CSS</sub>                 | CS Setup Time                                           | 5                            |     |     | 5          |     |     | ns    |

| t <sub>CSH</sub>                 | CS Hold Time                                            | 5                            |     |     | 5          |     |     | ns    |

| t <sub>SU</sub>                  | Data In Setup Time                                      | 2                            |     |     | 2          |     |     | ns    |

| t <sub>H</sub>                   | Data In Hold Time                                       | 3                            |     |     | 3          |     |     | ns    |

| t <sub>HO</sub>                  | Output Hold Time                                        | 0                            |     |     | 0          |     |     | ns    |

| t <sub>DIS</sub>                 | Output Disable Time                                     |                              |     | 8   |            |     | 6   | ns    |

| t <sub>v</sub>                   | Output Valid                                            |                              |     | 8   |            |     | 6   | ns    |

| t <sub>WPE</sub>                 | WP Low to Protection Enabled                            |                              |     | 1   |            |     | 1   | μs    |

| t <sub>WPD</sub>                 | WP High to Protection Disabled                          |                              |     | 1   |            |     | 1   | μs    |

| t <sub>EDPD</sub>                | CS High to Deep Power-down Mode                         |                              |     | 3   |            |     | 3   | μs    |

| t <sub>RDPD</sub>                | CS High to Standby Mode                                 |                              |     | 35  |            |     | 35  | μs    |

| t <sub>XFR</sub>                 | Page to Buffer Transfer Time                            |                              |     | 200 |            |     | 200 | μs    |

| t <sub>comp</sub>                | Page to Buffer Compare Time                             |                              |     | 200 |            |     | 200 | μs    |

| t <sub>EP</sub>                  | Page Erase and Programming Time (256/264 bytes)         |                              | 14  | 35  |            | 14  | 35  | ms    |

| t <sub>P</sub>                   | Page Programming Time (256/264 bytes)                   |                              | 2   | 4   |            | 2   | 4   | ms    |

| t <sub>PE</sub>                  | Page Erase Time (256/264 bytes)                         |                              | 13  | 32  |            | 13  | 32  | ms    |

| t <sub>BE</sub>                  | Block Erase Time (2,048/2,112 bytes)                    |                              | 30  | 75  |            | 30  | 75  | ms    |

| t <sub>SE</sub>                  | Sector Erase Time (65,536/67,584 bytes)                 |                              | 1.6 | 5   |            | 1.6 | 5   | S     |

| t <sub>CE</sub>                  | Chip Erase Time                                         |                              | 6   | 12  |            | 6   | 12  | s     |

| t <sub>RST</sub>                 | RESET Pulse Width                                       | 10                           |     |     | 10         |     |     | μs    |

| t <sub>REC</sub>                 | RESET Recovery Time                                     |                              |     | 1   |            |     | 1   | μs    |

### Table 18-4. AC Characteristics – RapidS/Serial Interface

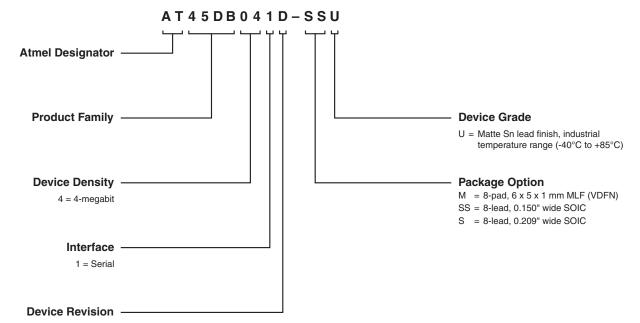

### 26. Ordering Information

### 26.1 Ordering Code Detail

### 26.2 Green Package Options (Pb/Halide-free/RoHS Compliant)

| Ordering Code <sup>(1)(2)</sup>     | Package | Lead Finish | Operating Voltage | f <sub>SCK</sub> (MHz) | Operation Range  |

|-------------------------------------|---------|-------------|-------------------|------------------------|------------------|

| AT45DB041D-MU                       |         |             |                   |                        |                  |

| AT45DB041D-MU-SL954 <sup>(3)</sup>  | 8M1-A   |             |                   |                        |                  |

| AT45DB041D-MU-SL955 <sup>(4)</sup>  |         |             |                   |                        |                  |

| AT45DB041D-SSU                      |         |             |                   |                        |                  |

| AT45DB041D-SSU-SL954 <sup>(3)</sup> | 8S1     | Matte Sn    | 2.7V to 3.6V      | 66                     |                  |

| AT45DB041D-SSU-SL955 <sup>(4)</sup> |         |             |                   |                        | Industrial       |

| AT45DB041D-SU                       |         |             |                   |                        | (-40°C to +85°C) |

| AT45DB041D-SU-SL954 <sup>(3)</sup>  | 8S2     |             |                   |                        |                  |

| AT45DB041D-SU-SL955 <sup>(4)</sup>  |         |             |                   |                        |                  |

| AT45DB041D-MU-2.5                   | 8M1-A   |             |                   |                        |                  |

| AT45DB041D-SSU-2.5                  | 8S1     | Matte Sn    | 25V to 3.6V       | 50                     |                  |

| AT45DB041D-SU-2.5                   | 8S2     | ]           |                   |                        |                  |

Notes: 1. The shipping carrier option is not marked on the devices.

2. Standard parts are shipped with the page size set to 264 bytes. The user is able to configure these parts to a 256-byte page size if desired.

3. Parts ordered with suffix SL954 are shipped in bulk with the page size set to 256 bytes. Parts will have a 954 or SL954 marked on them.

4. Parts ordered with suffix SL955 are shipped in tape and reel with the page size set to 256 bytes. Parts will have a 954 or SL954 marked on them.

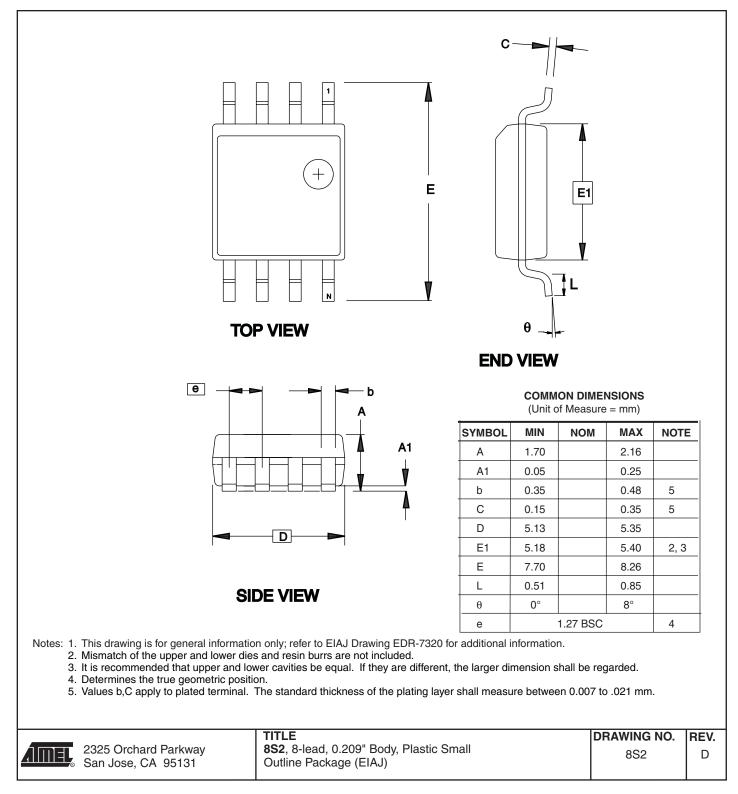

| Package Type |                                                                                          |  |

|--------------|------------------------------------------------------------------------------------------|--|

| 8M1-A        | 8-pad, 6 x 5 x 1.00 mm Body, Very Thin Dual Flat Package No Lead MLF <sup>™</sup> (VDFN) |  |

| 8S1          | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline Package (JEDEC SOIC)                |  |

| 8S2          | 8-lead, 0.209" Wide, Plastic Gull Wing Small Outline Package (EIAJ SOIC)                 |  |

#### 27.3 8S2 - EIAJ SOIC